Technology

High-performance error suppression for quantum computers

The foundational technology to achieve maximum performance on real quantum computer hardware

Errors undermine every quantum algorithm

Quantum computers are fundamentally error-prone. Decoherence, gate infidelity, and crosstalk degrade algorithmic outcomes and limit what today’s devices can achieve.

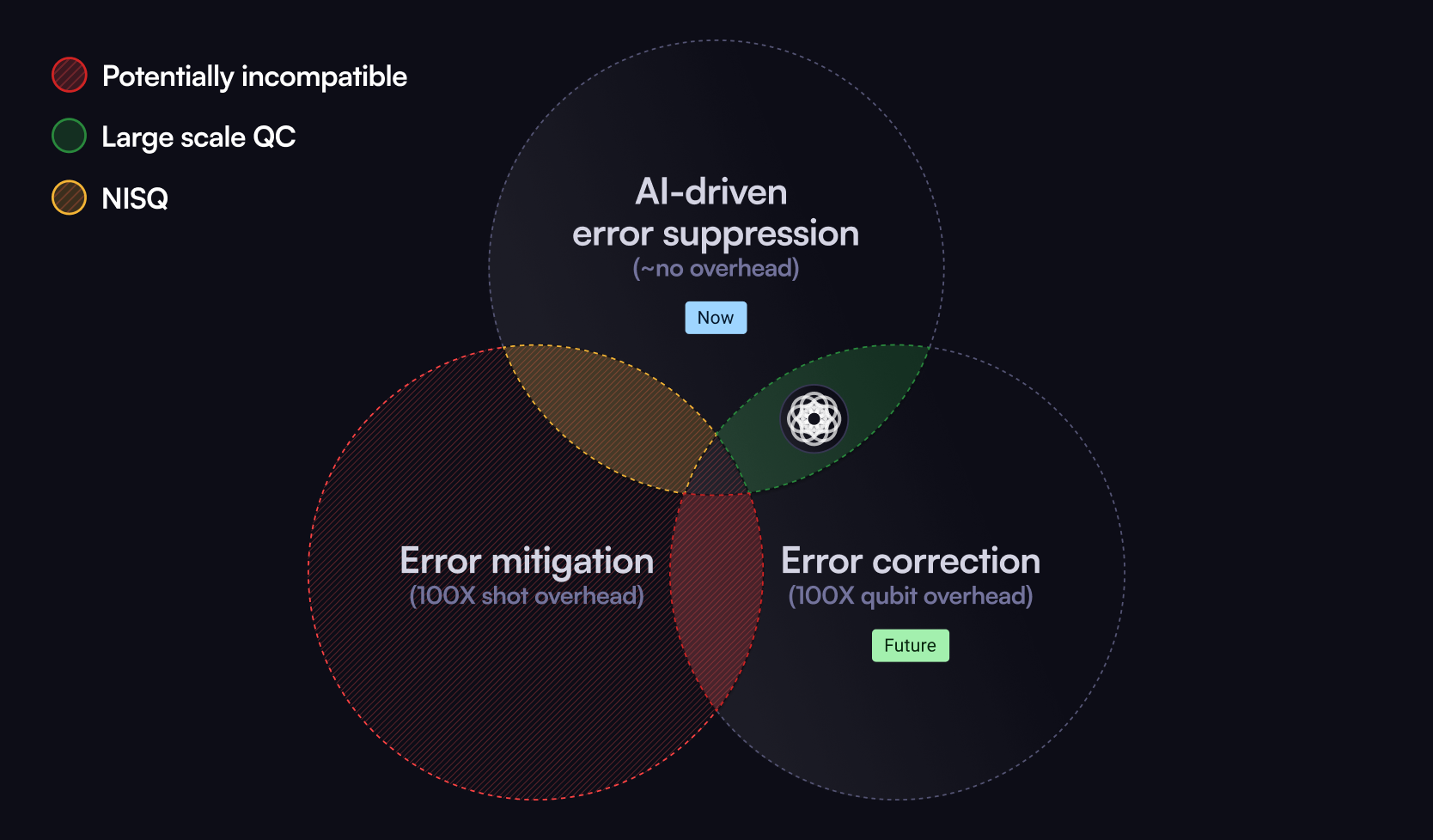

Quantum error correction (QEC) offers a long-term path to fault tolerance. But its extreme resource demands make it impractical today, and in many cases, it actually reduces system performance.

As a result, users struggle to achieve the meaningful insights required to justify larger investments into quantum computing. They’re not willing to wait and hope for future breakthroughs. A new solution is needed now to accelerate progress.

Suppress errors in any algorithm, even QEC, with automated and overhead-free technology

Q-CTRL’s proprietary error suppression technology helps quantum computers perform better from the start, without added hardware or added cost.

By reducing errors during qubit manipulation and memory operations, we build resilience directly into quantum hardware, instead of correcting issues after the fact.

This overhead-free technology dramatically improves quantum algorithm performance and is crucial given current constraints on hardware-system sizes and execution costs. And since QEC is itself an algorithm, error suppression has been shown to improve its ability to identify and correct errors, making these two technologies a perfectly complementary pair.

AI-powered hardware optimization and abstraction

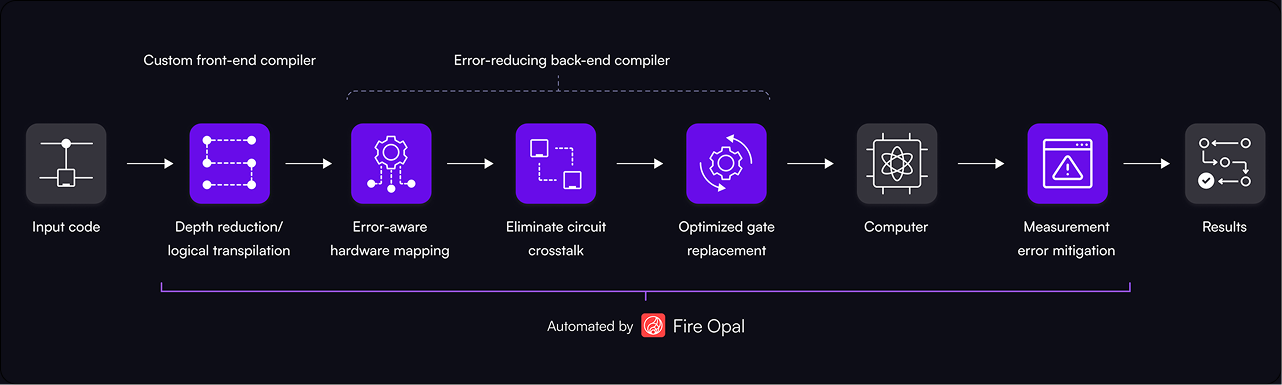

At Q-CTRL, we've redefined error suppression with an autonomous, integrated solution. With just a single line of code, our platform orchestrates every aspect of error suppression, from gate design to compilation delivering performance beyond traditional error mitigation.

Unlike mitigation techniques, our approach requires no pre-training and adds no runtime overhead. The result: lower execution costs and maximum performance from your hardware.

This entire stack comprises five key steps all tested and validated in the peer-reviewed literature, built and optimized for the underlying hardware and structured for seamless interoperability.

Key capabilities of FIRE Opal

An autonomous stack engineered for performance and compatibility

Delivered with a single line of code, our error suppression stack addresses every major source of error in quantum computation, at the level of compilation, layout selection, gate design, circuit execution, and measurement. Each layer is purpose-built for compatibility with real hardware and based on novel techniques developed by our team. Below are the key capabilities that distinguish Fire Opal.

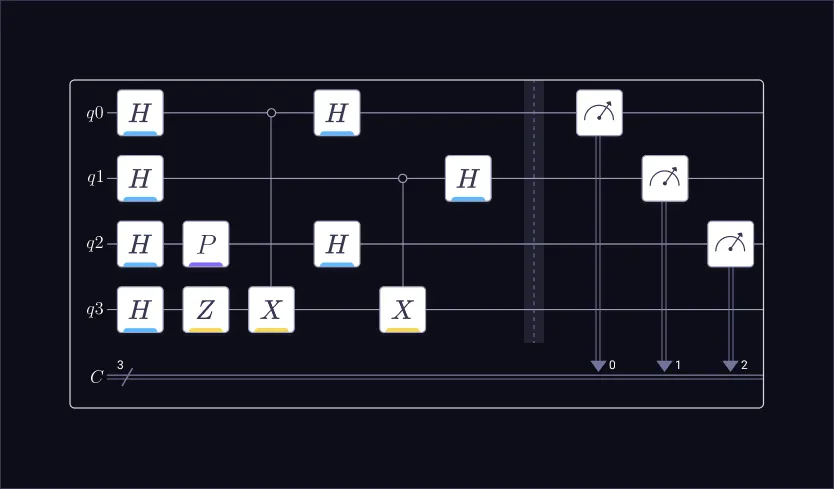

A custom compiler minimizes circuit depth and variability while maximizing compute speed

Quantum compilers are an essential part of the quantum computing stack: they take an abstract set of human-interpretable instructions and translate those into a hardware-compatible instruction set. Our compiler outperforms competitors in both speed and reliability, delivering superior performance for your quantum computations.

Reduces circuit depth and output variability

Integrates error-aware tactics into circuit generation

Speeds up compilation at scale without sacrificing quality

As we routinely execute circuits with 100 or more qubits, poorly crafted compilers are becoming a bottleneck in both computation time and output quality. Discover more about our benchmarks.

An abstract of four-qubit circuit for optimization.

An automated routine selects the

best-performing qubits for your algorithm

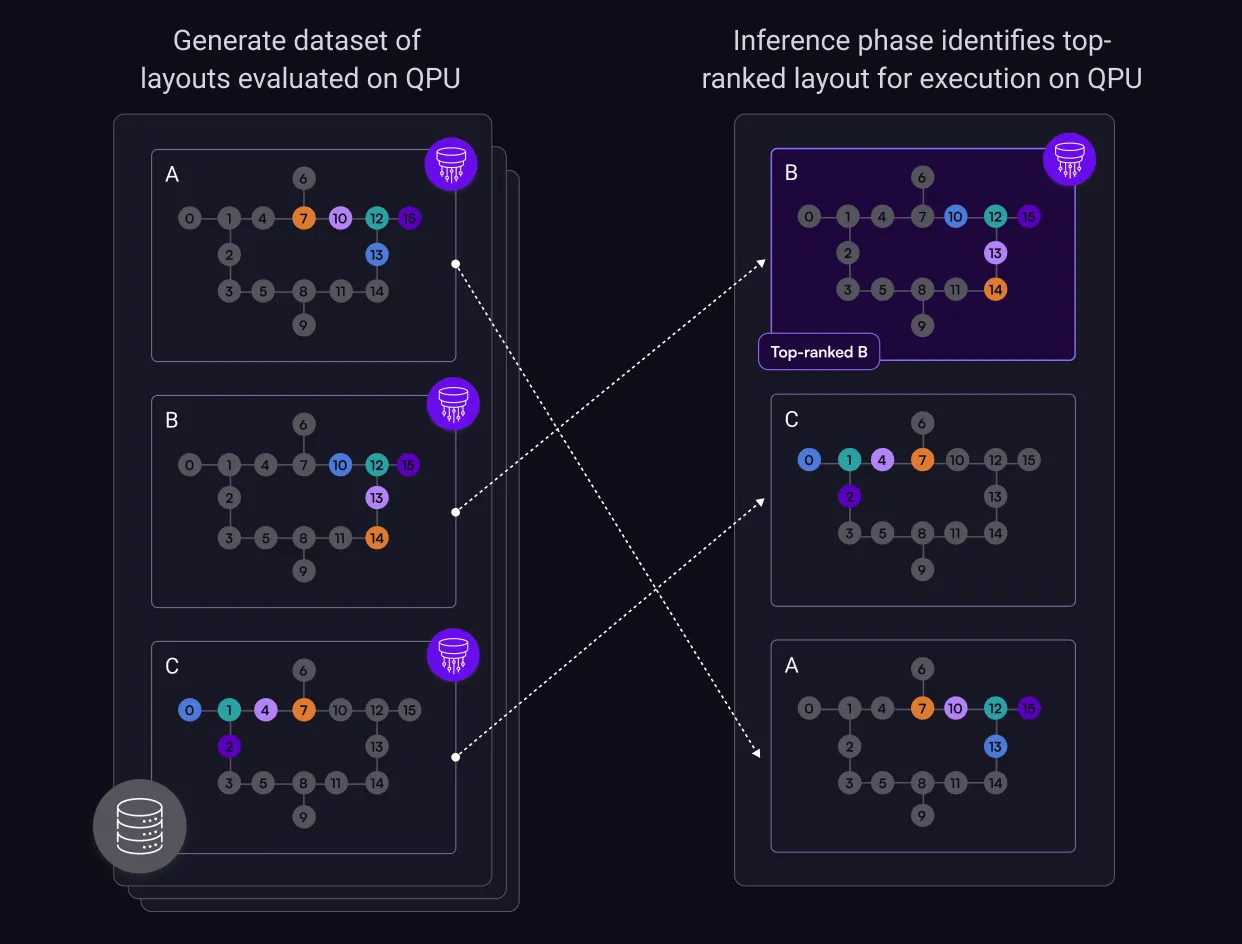

Most quantum algorithms only consume a fraction of the available computational resources (qubits), and performance variability between devices can span 10X or more. Choosing the right qubits for quantum algorithms is crucial, as poor selection can drastically reduce performance. An AI-based predictive quantum characterization routine solves this "layout selection" challenge, ranking potential qubit layouts for any circuit, ensuring optimal performance tailored to your algorithm.

Uses a physics-informed machine learning model for optimal qubit selection

Delivers >10X improvement with AI-powered prediction in ranking performance of different layouts

Enhances algorithmic fidelity by avoiding poor qubit choices

Learn more in our technical manuscript.

The machine learning pipeline uses a feedback loop between layout generation and hardware execution to train a model that can predict the best qubit layout for a quantum circuit.

Graph-based dynamical decoupling automatically interleaves optimized sequences into any input circuit for crosstalk and dephasing suppression

GraphDD uses a computational-graph structure representing the task of embedding DD protocols into all idle periods in an input circuit, accounting for the circuit structure and hardware details. The routine is automatic, efficient, and economical in the number of additional quantum logic operations, delivering over 1,000X improvement over standard DD embedding on real hardware.

Crosstalk suppression: Actively mitigates errors caused by unintended qubit interactions, accounting for relevant hardware interactions.

Dephasing suppression: Sequences are constructed to ensure single-qubit dynamics are suppressed simultaneously with crosstalk.

Automated and efficient: GraphDD intelligently finds the best circuit-wide decoupling protocol without numeric optimization, saving time and resources.

For further details, read our technical manuscript.

An illustration of a graph traversal process for automatic embedding of dynamical decoupling (DD). It illustrates how to systematically account for different contexts that occurs in a given circuit and embed optimal sequences of DD which simultaneously eliminates phase decoherence and cross-talk errors.

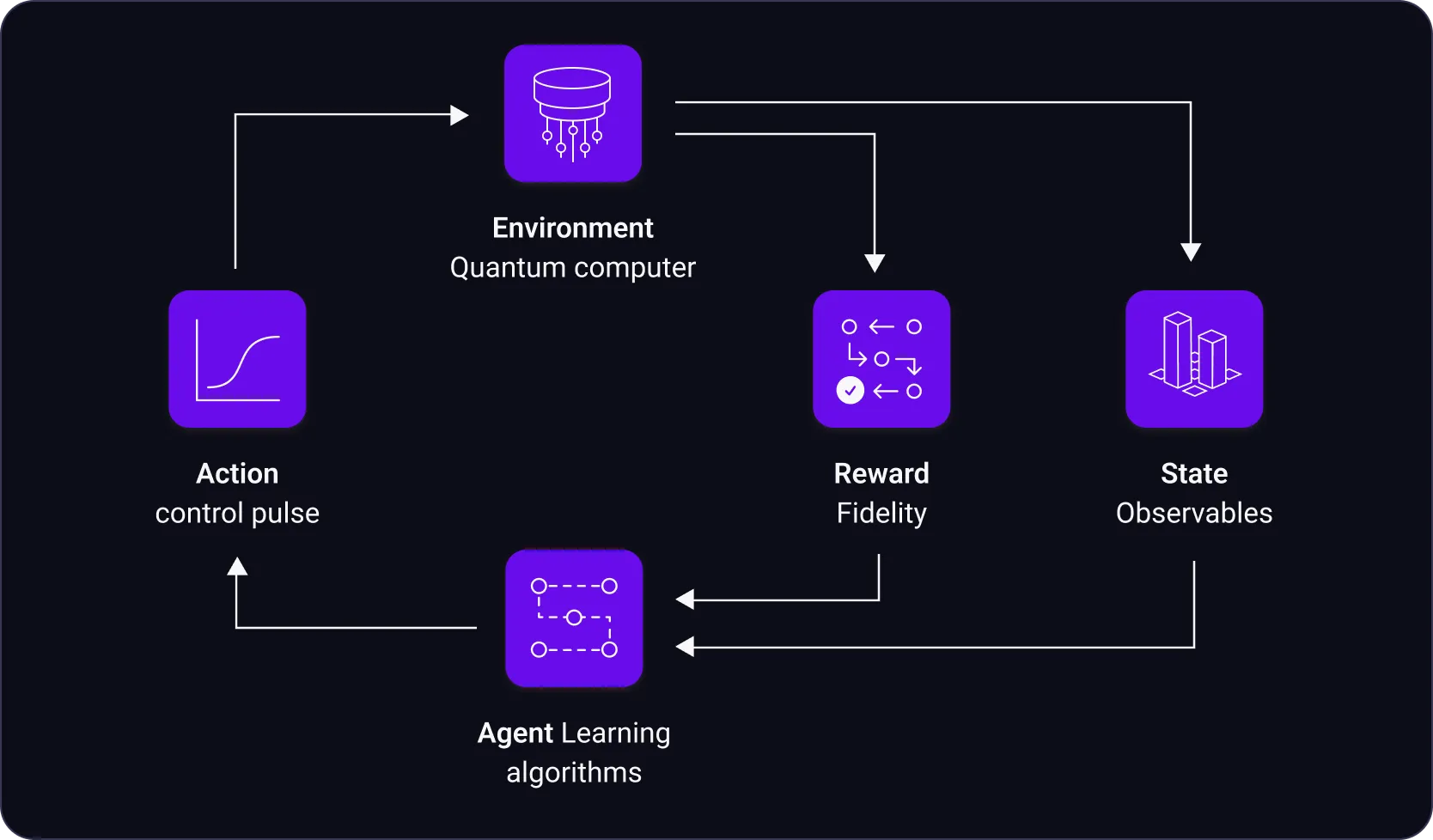

Closed-loop optimization delivers robust, error-resistant gate operations

Q-CTRL pioneered robust-control strategies designed to suppress errors in quantum logic. These techniques use underlying symmetries to cancel error accumulation from sources like calibration drifts and slowly fluctuating fields. Validated across various hardware platforms, including superconducting qubits and trapped ions, they can outperform analytically designed solutions through AI-driven optimization.

Autonomous gate optimization: Our AI-driven protocol designs optimized gate waveforms automatically, requiring no prior device knowledge or human intervention.

Parallelized optimization: Efficiently optimizes all gates on the hardware system in parallel, considering device topology.

Seamless background operation: Optimizations run behind the scenes, providing a lookup table of enhanced gate definitions for improved circuit performance, without user intervention.

Learn more about our pioneering research on automated gate design using machine learning.

This diagram illustrates a Deep Reinforcement Learning (DRL) optimization process on quantum hardware, where a model iteratively improves control pulses by collecting real-time quantum state estimations and using that data to maximize a long-term reward function.

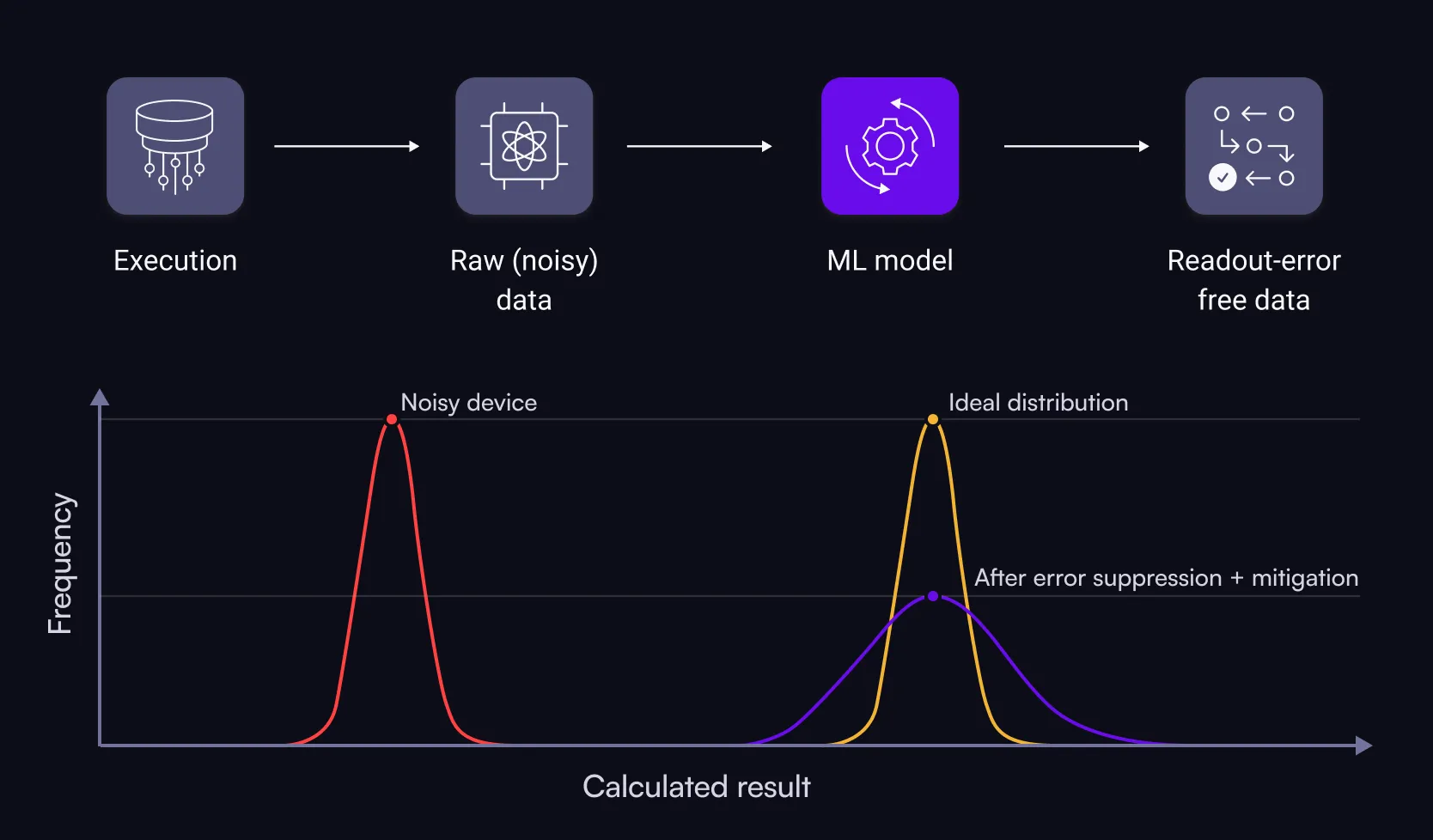

Efficient signal processing reduces the impact of readout errors

A custom neural-network-based measurement error mitigation protocol corrects readout errors. It divides the device into smaller, optimally chosen qubit groups for correction, then feeds outputs into a neural network to restore correlations, capture non-linear effects, and handle contextual errors.

The process scales sub-linearly with qubit count, minimizing training data. An AI-driven calibration routine identifies error processes and, at runtime, combines this data with measurements to estimate output probabilities and confidence intervals efficiently.

Tensored mitigation efficiently corrects readout errors by dividing qubits into optimally chosen, smaller groups reflecting hardware architecture.

Neural network refinement restores neglected correlations, accounts for nonlinearities, and handles contextual errors beyond traditional methods.

AI-driven calibration and runtime processing minimize overhead, scaling qubit count for fast, accurate results.

A custom neural-network-based measurement error mitigation protocol corrects readout errors, delivering readout-error free data.

Why ERROR SUPPRESION

The key to unlocking useful quantum error correction

The combination of quantum error suppression and quantum error correction is essential to achieving practically relevant QEC which scales efficiently in terms of hardware resource requirements. Because it’s so resource intensive, we have to do everything we can to improve baseline error rates prior to applying QEC.

Applying QEC without suppression is like cooling a room with the windows open, you’ll use a lot of energy without much effect. Error suppression “closes the windows and adds insulation,” allowing QEC to work efficiently and deliver meaningful gains. When combined, suppression and correction form a scalable pathway to fault tolerance, which brings useful quantum computing closer to reality.

Better than this analogy is the evidence we already have in hand. Three separate manuscripts from Nord Quantique, the University of Sydney, and Q-CTRL show how the combination of error suppression technologies with QEC encoding make QEC perform better – whether in the quality of logical encoding or QEC’s ability to actually identify and correct errors.

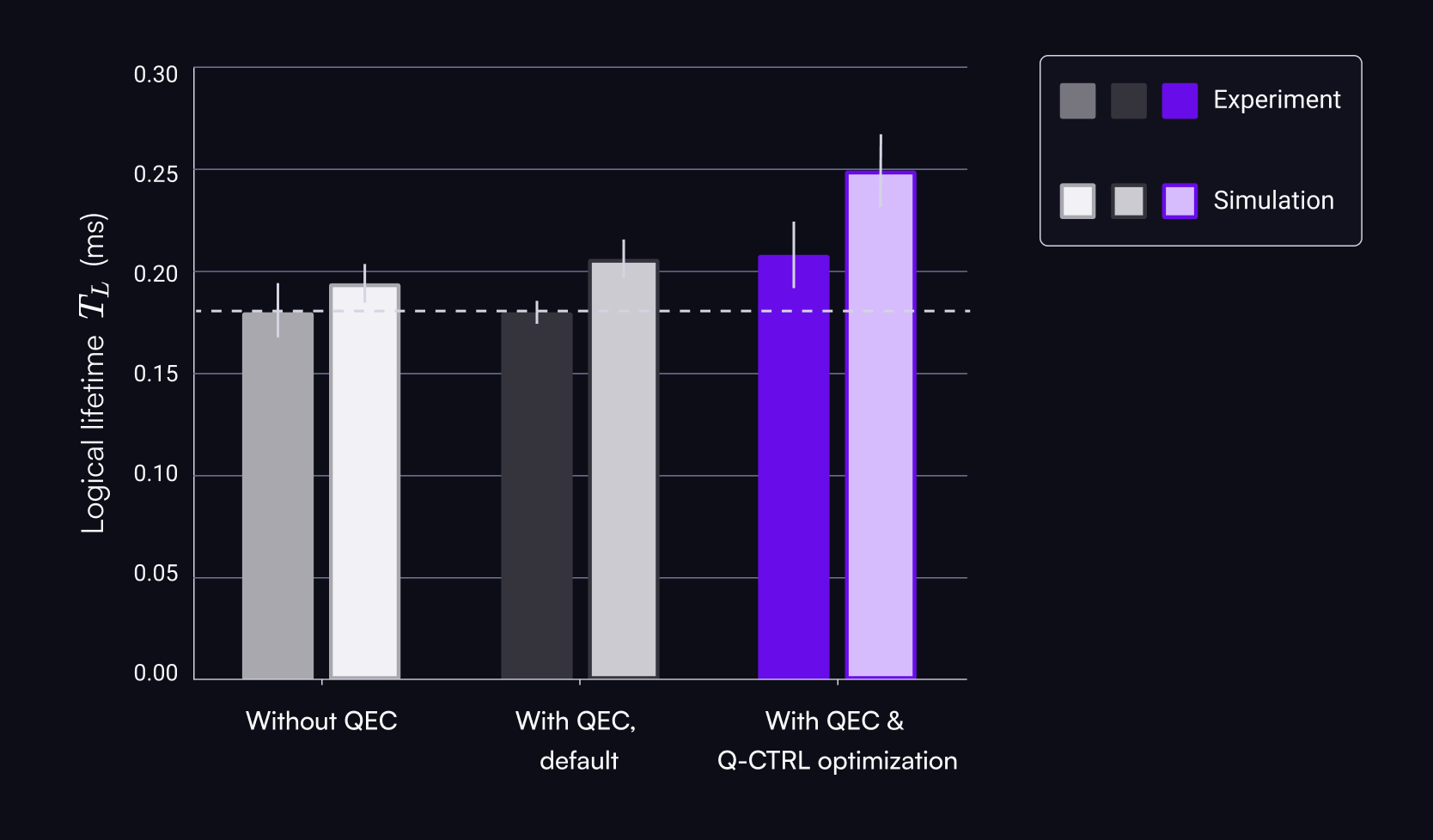

In Nord Quantique’s work, the inclusion of our technology for hardware optimization meant the difference between achieving only breakeven performance with QEC or actually achieving a net enhancement in logical qubit lifetime!

Techniques validated to set the world standard

Q-CTRL’s error suppression technologies are validated in the open literature to deliver the best performance achievable on today’s hardware. Nothing else comes close. Explore our benchmarks for up-to-date performance estimates.

10X

Deeper circuits

1,000X

Reduced compute costs

1,000X

Improved accuracy

Get started now

Make quantum technology useful